#### HIGHLIGHTS

This section of the manual contains the following major topics:

| 29.1 | Introduction                                     |  |

|------|--------------------------------------------------|--|

| 29.2 | Instruction Formats                              |  |

| 29.3 | Special Function Registers as Source/Destination |  |

| 29.4 | Q Cycle Activity                                 |  |

|      | Instruction Descriptions                         |  |

| 29.6 | Design Tips                                      |  |

| 29.7 | Related Application Notes                        |  |

| 29.8 | Revision History                                 |  |

#### 29.1 Introduction

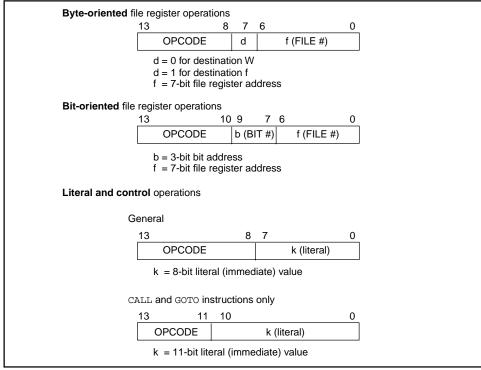

Each midrange instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The midrange Instruction Set Summary in Table 29-1 lists the instructions recognized by the MPASM assembler. The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Table 29-2 gives the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For literal and control operations, 'k' represents an eight or eleven bit constant or literal value.

All instructions are executed in one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In these cases, the execution takes two instruction cycles with the second cycle executed as an NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

|                       | 14 Dit Instruction Word |                                     |        |                         |      |      |      |          |       |  |

|-----------------------|-------------------------|-------------------------------------|--------|-------------------------|------|------|------|----------|-------|--|

| Mnemonic,<br>Operands |                         | Description                         | Cycles | 14-Bit Instruction Word |      |      |      | Status   | Notes |  |

|                       |                         | •                                   |        | MSb                     |      |      | LSb  | Affected |       |  |

| BYTE-ORIEN            | ITED FI                 | LE REGISTER OPERATIONS              |        |                         |      |      |      |          |       |  |

| ADDWF                 | f, d                    | Add W and f                         | 1      | 00                      | 0111 | dfff | ffff | C,DC,Z   | 1,2   |  |

| ANDWF                 | f, d                    | AND W with f                        | 1      | 00                      | 0101 | dfff | ffff | Z        | 1,2   |  |

| CLRF                  | f                       | Clear f                             | 1      | 00                      | 0001 | lfff | ffff | Z        | 2     |  |

| CLRW                  | -                       | Clear W                             | 1      | 00                      | 0001 | 0xxx | XXXX | Z        |       |  |

| COMF                  | f, d                    | Complement f                        | 1      | 00                      | 1001 | dfff | ffff | Z        | 1,2   |  |

| DECF                  | f, d                    | Decrement f                         | 1      | 00                      | 0011 | dfff | ffff | Z        | 1,2   |  |

| DECFSZ                | f, d                    | Decrement f, Skip if 0              | 1(2)   | 00                      | 1011 | dfff | ffff |          | 1,2,3 |  |

| INCF                  | f, d                    | Increment f                         | 1      | 00                      | 1010 | dfff | ffff | Z        | 1,2   |  |

| INCFSZ                | f, d                    | Increment f, Skip if 0              | 1(2)   | 00                      | 1111 | dfff | ffff |          | 1,2,3 |  |

| IORWF                 | f, d                    | Inclusive OR W with f               | 1      | 00                      | 0100 | dfff | ffff | Z        | 1,2   |  |

| MOVF                  | f, d                    | Move f                              | 1      | 00                      | 1000 | dfff | ffff | Z        | 1,2   |  |

| MOVWF                 | f                       | Move W to f                         | 1      | 00                      | 0000 | lfff | ffff |          |       |  |

| NOP                   | -                       | No Operation                        | 1      | 00                      | 0000 | 0xx0 | 0000 |          |       |  |

| RLF                   | f, d                    | Rotate Left f through Carry         | 1      | 00                      | 1101 | dfff | ffff | С        | 1,2   |  |

| RRF                   | f, d                    | Rotate Right f through Carry        | 1      | 00                      | 1100 | dfff | ffff | С        | 1,2   |  |

| SUBWF                 | f, d                    | Subtract W from f                   | 1      | 00                      | 0010 | dfff | ffff | C,DC,Z   | 1,2   |  |

| SWAPF                 | f, d                    | Swap nibbles in f                   | 1      | 00                      | 1110 | dfff | ffff |          | 1,2   |  |

| XORWF                 | f, d                    | Exclusive OR W with f               | 1      | 00                      | 0110 | dfff | ffff | z        | 1,2   |  |

| <b>BIT-ORIENTE</b>    | D FILE                  | REGISTER OPERATIONS                 |        |                         |      |      |      |          |       |  |

| BCF                   | f, b                    | Bit Clear f                         | 1      | 01                      | 00bb | bfff | ffff |          | 1,2   |  |

| BSF                   | f, b                    | Bit Set f                           | 1      | 01                      | 01bb | bfff | ffff |          | 1,2   |  |

| BTFSC                 | f, b                    | Bit Test f, Skip if Clear           | 1 (2)  | 01                      | 10bb | bfff | ffff |          | 3     |  |

| BTFSS                 | f, b                    | Bit Test f, Skip if Set             | 1 (2)  | 01                      | 11bb | bfff | ffff |          | 3     |  |

| LITERAL AN            | D CON                   | TROL OPERATIONS                     |        |                         |      |      |      |          |       |  |

| ADDLW                 | k                       | Add literal and W                   | 1      | 11                      | 111x | kkkk | kkkk | C,DC,Z   |       |  |

| ANDLW                 | k                       | AND literal with W                  | 1      | 11                      | 1001 | kkkk | kkkk | Z        |       |  |

| CALL                  | k                       | Call subroutine                     | 2      | 10                      | 0kkk | kkkk | kkkk |          |       |  |

| CLRWDT                | -                       | Clear Watchdog Timer                | 1      | 00                      | 0000 | 0110 | 0100 | TO,PD    |       |  |

| GOTO                  | k                       | Go to address                       | 2      | 10                      | 1kkk | kkkk | kkkk | ,        |       |  |

| IORLW                 | k                       | Inclusive OR literal with W         | 1      | 11                      | 1000 | kkkk | kkkk | z        |       |  |

| MOVLW                 | k                       | Move literal to W                   | 1      | 11                      | 00xx | kkkk | kkkk |          |       |  |

| RETFIE                | -                       | Return from interrupt               | 2      | 00                      | 0000 | 0000 | 1001 |          |       |  |

| RETLW                 | k                       | Return with literal in W            | 2      | 11                      | 01xx | kkkk | kkkk |          |       |  |

| RETURN                | -                       | Return from Subroutine              | 2      | 00                      | 0000 | 0000 | 1000 |          |       |  |

| SLEEP                 | -                       | Go into standby mode                | 1      | 00                      | 0000 | 0110 | 0011 | TO,PD    |       |  |

| SUBLW                 | k                       | Subtract W from literal             | 1      | 11                      | 110x | kkkk | kkkk | C,DC,Z   |       |  |

| XORLW                 | k                       | Exclusive OR literal with W         | 1      | 11                      | 1010 | kkkk | kkkk |          |       |  |

|                       |                         | Exclusive of medified as a function |        |                         |      |      |      |          | 1     |  |

| Table 29-1: Midran | ge Instruction Set |

|--------------------|--------------------|

|--------------------|--------------------|

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP. 29

#### 29.2 Instruction Formats

Figure 29-1 shows the three general formats that the instructions can have. As can be seen from the general format of the instructions, the opcode portion of the instruction word varies from 3-bits to 6-bits of information. This is what allows the midrange instruction set to have 35 instructions.

**Note 1:** Any unused opcode is Reserved. Use of any reserved opcode may cause unexpected operation.

**Note 2:** To maintain upward compatibility with future midrange products, <u>do not use</u> the OPTION and TRIS instructions.

All instruction examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

To represent a binary number:

00000100b

where b is a binary string identifier.

#### Figure 29-1: General Format for Instructions

| Field         | Description                                                                                                                                                   |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                          |

| W             | Working register (accumulator)                                                                                                                                |

| b             | Bit address within an 8-bit file register (0 to 7)                                                                                                            |

| k             | Literal field, constant data or label (may be either an 8-bit or an 11-bit value)                                                                             |

| х             | Don't care (0 or 1)<br>The assembler will generate code with $x = 0$ . It is the recommended form of use for compatibility with all Microchip software tools. |

| d             | Destination select;<br>d = 0: store result in W,<br>d = 1: store result in file register f.                                                                   |

| dest          | Destination either the W register or the specified register file location                                                                                     |

| label         | Label name                                                                                                                                                    |

| TOS           | Top of Stack                                                                                                                                                  |

| PC            | Program Counter                                                                                                                                               |

| PCLATH        | Program Counter High Latch                                                                                                                                    |

| GIE           | Global Interrupt Enable bit                                                                                                                                   |

| WDT           | Watchdog Timer                                                                                                                                                |

| TO            | Time-out bit                                                                                                                                                  |

| PD            | Power-down bit                                                                                                                                                |

| []            | Optional                                                                                                                                                      |

| ()            | Contents                                                                                                                                                      |

| $\rightarrow$ | Assigned to                                                                                                                                                   |

| < >           | Register bit field                                                                                                                                            |

| E             | In the set of                                                                                                                                                 |

| italics       | User defined term (font is courier)                                                                                                                           |

#### 29.3 Special Function Registers as Source/Destination

The Section 29. Instruction Set's orthogonal instruction set allows read and write of all file registers, including special function registers. Some special situations the user should be aware of are explained in the following subsections:

#### 29.3.1 STATUS Register as Destination

If an instruction writes to the STATUS register, the Z, C, DC and OV bits may be set or cleared as a result of the instruction and overwrite the original data bits written. For example, executing CLRF STATUS will clear register STATUS, and then set the Z bit leaving 0000 0100b in the register.

#### 29.3.2 PCL as Source or Destination

Read, write or read-modify-write on PCL may have the following results:

| Read PC:           | $PCL \to dest;$                                                                                                    | PCLATH does not change;          |

|--------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Write PCL:         | PCLATH $\rightarrow$ P<br>8-bit destination                                                                        | CH;<br>on value $ ightarrow$ PCL |

| Read-Modify-Write: | $\begin{array}{l} PCL \rightarrow ALU \text{ op} \\ PCLATH \rightarrow PC \\ 8-bit result \rightarrow \end{array}$ | CH;                              |

Where PCH = program counter high byte (not an addressable register), PCLATH = Program counter high holding latch, dest = destination, W register or register file f.

#### 29.3.3 Bit Manipulation

All bit manipulation instructions will first read the entire register, operate on the selected bit and then write the result back (read-modify-write (R-M-W)) the specified register. The user should keep this in mind when operating on some special function registers, such as ports.

**Note:** Status bits that are manipulated by the device (including the interrupt flag bits) are set or cleared in the Q1 cycle. So there is no issue with executing R-M-W instructions on registers which contain these bits.

#### 29.4 Q Cycle Activity

Each instruction cycle (Tcy) is comprised of four Q cycles (Q1-Q4). The Q cycle is the same as the device oscillator cycle (Tosc). The Q cycles provide the timing/designation for the Decode, Read, Process Data, Write etc., of each instruction cycle. The following diagram shows the relationship of the Q cycles to the instruction cycle.

The four Q cycles that make up an instruction cycle (Tcy) can be generalized as:

- Q1: Instruction Decode Cycle or forced No Operation

- Q2: Instruction Read Cycle or No Operation

- Q3: Process the Data

- Q4: Instruction Write Cycle or No Operation

Each instruction will show the detailed Q cycle operation for the instruction.

####

#### Figure 29-2: Q Cycle Activity

#### 29.5 Instruction Descriptions

| ADDLW             | Add Literal and W                                                                                                 |

|-------------------|-------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] ADDLW k                                                                                          |

| Operands:         | $0 \le k \le 255$                                                                                                 |

| Operation:        | $(W) \textbf{+} k \to W$                                                                                          |

| Status Affected:  | C, DC, Z                                                                                                          |

| Encoding:         | 11 111x kkkk kkkk                                                                                                 |

| Description:      | The contents of the W register are added to the eight bit literal 'k' and the result is placed in the W register. |

| Words:            | 1                                                                                                                 |

| Cycles:           | 1                                                                                                                 |

| Q Cycle Activity: |                                                                                                                   |

| Q1                | Q2 Q3 Q4                                                                                                          |

| Decode            | Read     Process     Write to W       literal 'k'     data     register                                           |

|                   |                                                                                                                   |

| Example1          | ADDLW 0x15                                                                                                        |

| Example i         | Before Instruction                                                                                                |

|                   | W = 0x10                                                                                                          |

|                   | After Instruction                                                                                                 |

|                   | W = 0x25                                                                                                          |

| Example 2         | ADDLW MYREG                                                                                                       |

|                   | Before Instruction                                                                                                |

|                   | $W = 0 \times 10$                                                                                                 |

|                   | Address of MYREG <sup>†</sup> = 0x37<br>† MYREG is a symbol for a data memory location                            |

|                   | After Instruction                                                                                                 |

|                   | W = 0x47                                                                                                          |

| Example 3         | ADDLW HIGH (LU_TABLE)                                                                                             |

|                   | Before Instruction                                                                                                |

|                   | $W = 0 \times 10$                                                                                                 |

|                   | Address of LU_TABLE $\dagger = 0x9375$                                                                            |

|                   | † LU_TABLE is a label for an address in program memory<br>After Instruction                                       |

|                   | W = 0xA3                                                                                                          |

|                   |                                                                                                                   |

| Example 4         | ADDLW MYREG                                                                                                       |

|                   | Before Instruction<br>W = 0x10                                                                                    |

|                   | W = 0x10<br>Address of PCL <sup>†</sup> = 0x02                                                                    |

|                   | $\dagger  {\tt PCL}$ is the symbol for the Program Counter low byte location                                      |

|                   | After Instruction<br>W = 0x12                                                                                     |

|                   | W = 0x12                                                                                                          |

| -                 |                                                                                                                                                                 |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ]ADDWF f,d                                                                                                                                       |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |

| Operation:        | (W) + (f) $\rightarrow$ destination                                                                                                                             |

| Status Affected:  | C, DC, Z                                                                                                                                                        |

| Encoding:         | 00 0111 dfff ffff                                                                                                                                               |

| Description:      | Add the contents of the W register with register 'f'. If 'd' is 0 the result is stored in th W register. If 'd' is 1 the result is stored back in register 'f'. |

| Words:            | 1                                                                                                                                                               |

| Cycles:           | 1                                                                                                                                                               |

| Q Cycle Activity: |                                                                                                                                                                 |

| Q1                | Q2 Q3 Q4                                                                                                                                                        |

| Decode            | Read Process Write to                                                                                                                                           |

|                   | register 'f' data destination                                                                                                                                   |

|                   |                                                                                                                                                                 |

| Example 1         | ADDWF FSR, 0                                                                                                                                                    |

|                   | Before Instruction                                                                                                                                              |

|                   | W = 0x17                                                                                                                                                        |

|                   | FSR = 0xC2<br>After Instruction                                                                                                                                 |

|                   | W = 0xD9                                                                                                                                                        |

|                   | FSR = 0xC2                                                                                                                                                      |

|                   |                                                                                                                                                                 |

| Example 2         | ADDWF INDF, 1                                                                                                                                                   |

|                   | Before Instruction                                                                                                                                              |

|                   | W = 0x17<br>FSR = 0xC2                                                                                                                                          |

|                   | Contents of Address (FSR) = 0x20                                                                                                                                |

|                   | After Instruction                                                                                                                                               |

|                   | W = 0x17<br>FSR = 0xC2                                                                                                                                          |

|                   | Contents of Address (FSR) = 0x37                                                                                                                                |

|                   |                                                                                                                                                                 |

| Example 3         | ADDWF PCL                                                                                                                                                       |

| Case 1:           | Before Instruction                                                                                                                                              |

|                   | W = 0x10 PCL = 0x37                                                                                                                                             |

|                   | C = X                                                                                                                                                           |

|                   | After Instruction                                                                                                                                               |

|                   | PCL = 0x47 $C = 0$                                                                                                                                              |

| Case 2:           | Before Instruction                                                                                                                                              |

| Case 2.           | Before instruction $W = 0x10$                                                                                                                                   |

|                   | PCL = 0xF7                                                                                                                                                      |

|                   | PCH = 0x08                                                                                                                                                      |

|                   | C = x<br>After Instruction                                                                                                                                      |

|                   | PCL = 0x07                                                                                                                                                      |

|                   | PCH = 0x08                                                                                                                                                      |

|                   | c = 1                                                                                                                                                           |

Instruction Set

| ANDLW             | And Literal with W                                                                                                                                                                                         |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] ANDLW k                                                                                                                                                                                   |

| Operands:         | $0 \le k \le 255$                                                                                                                                                                                          |

| Operation:        | (W).AND. (k) $\rightarrow$ W                                                                                                                                                                               |

| Status Affected:  | Z                                                                                                                                                                                                          |

| Encoding:         | 11 1001 kkkk kkkk                                                                                                                                                                                          |

| Description:      | The contents of W register are AND'ed with the eight bit literal 'k'. The result is placed in the W register.                                                                                              |

| Words:            | 1                                                                                                                                                                                                          |

| Cycles:           | 1                                                                                                                                                                                                          |

| Q Cycle Activity: |                                                                                                                                                                                                            |

| Q1                | Q2 Q3 Q4                                                                                                                                                                                                   |

| Decode            | Read literal Process Write to W<br>'k' data register                                                                                                                                                       |

|                   | W = 0xA3       ; 1010 0011 (0xA3)         After Instruction       ;         W = 0x03       ; 0000 0011 (0x03)                                                                                              |

| Example 2         | ANDLW MYREG                                                                                                                                                                                                |

|                   | Before Instruction<br>W = 0xA3<br>Address of MYREG <sup>†</sup> = 0x37<br><sup>†</sup> MYREG is a symbol for a data memory location<br>After Instruction<br>W = 0x23                                       |

| Example 3         | ANDLW HIGH (LU_TABLE)<br>Before Instruction<br>W = 0xA3<br>Address of LU_TABLE <sup>†</sup> = 0x9375<br><sup>†</sup> LU_TABLE is a label for an address in program memory<br>After Instruction<br>W = 0x83 |

| A     | NDWF          | AND W with f                                                                                                                                                                         |

|-------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synt  | ax:           | [ <i>label</i> ] ANDWF f,d                                                                                                                                                           |

| Ope   | rands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                   |

| Ope   | ration:       | (W).AND. (f) $\rightarrow$ destination                                                                                                                                               |

| Statu | us Affected:  | Ζ                                                                                                                                                                                    |

| Enco  | oding:        | 00 0101 dfff ffff                                                                                                                                                                    |

| Desc  | cription:     | AND the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If<br>'d' is 1 the result is stored back in register 'f'.                                  |

| Word  | ds:           | 1                                                                                                                                                                                    |

| Cycl  | es:           | 1                                                                                                                                                                                    |

| QC    | cle Activity: |                                                                                                                                                                                      |

|       | Q1            | Q2 Q3 Q4                                                                                                                                                                             |

|       | Decode        | Read Process Write to<br>register 'f' data destination                                                                                                                               |

|       |               | W = 0x17 		; 1100 	0010 	(0xC2)                                                                                                                                                      |

| Exar  | mple 2        | ANDWF FSR, 0<br>Before Instruction ; 0001 0111 (0x17)<br>W = 0x17 ; 1100 0010 (0xC2)<br>FSR = 0xC2 ;<br>After Instruction ; 0000 0010 (0x02)<br>W = 0x02<br>FSR = 0xC2               |

| Exar  | mple 3        | ANDWF INDF, 1<br>Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>Contents of Address (FSR) = 0x5A<br>After Instruction<br>W = 0x17<br>FSR = 0xC2<br>Contents of Address (FSR) = 0x15 |

| BCF               | Bit Clear f                                                                                                                     |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] BCF f,b                                                                                                        |

| Operands:         | $0 \le f \le 127$ $0 \le b \le 7$                                                                                               |

| Operation:        | $0 \rightarrow f < b >$                                                                                                         |

| Status Affected:  | None                                                                                                                            |

| Encoding:         | 01 00bb bfff ffff                                                                                                               |

| Description:      | Bit 'b' in register 'f' is cleared.                                                                                             |

| Words:            | 1                                                                                                                               |

| Cycles:           | 1                                                                                                                               |

| Q Cycle Activity: |                                                                                                                                 |

| Q1                | Q2 Q3 Q4                                                                                                                        |

| Decode            | ReadProcessWriteregister 'f'dataregister 'f'                                                                                    |

| Example 1         | BCF FLAG_REG, 7                                                                                                                 |

|                   | Before Instruction<br>FLAG_REG = 0xC7 ; 1100 0111                                                                               |

|                   | After Instruction                                                                                                               |

|                   | FLAG_REG = 0x47 ; 0100 0111                                                                                                     |

| Example 2         | BCF INDF, 3                                                                                                                     |

|                   | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>Contents of Address (FSR) = 0x2F<br>After Instruction<br>W = 0x17<br>FSR = 0xC2 |

| BS    | SF            | E                                 | Bit Set f                               |      |                     |                |        |  |  |

|-------|---------------|-----------------------------------|-----------------------------------------|------|---------------------|----------------|--------|--|--|

| Synta | ax:           | [ <i>label</i> ] B                | SF f,b                                  |      |                     |                |        |  |  |

| Oper  | ands:         | $0 \le f \le 127$ $0 \le b \le 7$ | 7                                       |      |                     |                |        |  |  |

| Oper  | ation:        | $1 \rightarrow \text{f}$          |                                         |      |                     |                |        |  |  |

| Statu | s Affected:   | None                              |                                         |      |                     |                |        |  |  |

| Enco  | ding:         | 01                                | 01bb bf                                 | ff   | ffff                |                |        |  |  |

| Desc  | ription:      | Bit 'b' in re                     | gister 'f' is s                         | et.  |                     | 1              |        |  |  |

| Word  | ls:           | 1                                 |                                         |      |                     |                |        |  |  |

| Cycle | es:           | 1                                 |                                         |      |                     |                |        |  |  |

| Q Cy  | cle Activity: |                                   |                                         |      |                     |                |        |  |  |

| _     | Q1            | Q2                                | Q3                                      | Q4   |                     | _              |        |  |  |

|       | Decode        | Read<br>register 'f'              | Process<br>data                         |      | Write<br>gister 'f' |                |        |  |  |

| Exan  | nple 1        | BSF                               | FLAG_REG,                               | 7    |                     |                |        |  |  |

|       |               | Before Ins<br>F                   | truction<br>LAG_REG =0                  | 0x0A |                     | ; <b>0</b> 000 | 1010   |  |  |

|       |               | After Instr                       | uction                                  |      |                     |                |        |  |  |

|       |               | F                                 | LAG_REG =0                              | 0x8A |                     | ; 1000         | 0 1010 |  |  |

| Exan  | nple 2        | BSF                               | INDF, 3                                 |      |                     |                |        |  |  |

|       |               | F<br>C<br>After Instr<br>V<br>F   | V = 0x17<br>SR = 0xC2<br>Contents of Ac |      |                     |                |        |  |  |

| BTFSC               | В                                                                                         | it Test, S                                                                                                                                                                                                                                                     | kip if C           | lear           |  |  |

|---------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|--|--|

| Syntax:             | [ <i>label</i> ] BT                                                                       | FSC f,b                                                                                                                                                                                                                                                        |                    |                |  |  |

| Operands:           | $0 \le f \le 127$                                                                         |                                                                                                                                                                                                                                                                |                    |                |  |  |

|                     | $0 \le b \le 7$                                                                           |                                                                                                                                                                                                                                                                |                    |                |  |  |

| Operation:          | skip if (f <b:< td=""><td colspan="5">skip if <math>(f &lt; b &gt;) = 0</math></td></b:<> | skip if $(f < b >) = 0$                                                                                                                                                                                                                                        |                    |                |  |  |

| Status Affected:    | None                                                                                      |                                                                                                                                                                                                                                                                |                    |                |  |  |

| Encoding:           | 01                                                                                        | 10bb                                                                                                                                                                                                                                                           | bfff               | ffff           |  |  |

| Description:        | If bit 'b' is '0'                                                                         | If bit 'b' in register 'f' is '0' then the next instruction is skipped.<br>If bit 'b' is '0' then the next instruction (fetched during the current instruction execu-<br>tion) is discarded, and a NOP is executed instead, making this a 2 cycle instruction. |                    |                |  |  |

| Words:              | 1                                                                                         |                                                                                                                                                                                                                                                                |                    |                |  |  |

| Cycles:             | 1(2)                                                                                      |                                                                                                                                                                                                                                                                |                    |                |  |  |

| Q Cycle Activity:   |                                                                                           |                                                                                                                                                                                                                                                                |                    |                |  |  |

| Q1                  | Q2                                                                                        | Q3                                                                                                                                                                                                                                                             | Q4                 | ŀ              |  |  |

| Decode              | Read<br>register 'f'                                                                      | Proces<br>data                                                                                                                                                                                                                                                 | -                  | No<br>peration |  |  |

| If skip (2nd cycle) |                                                                                           |                                                                                                                                                                                                                                                                | 0                  | peration       |  |  |

| Q1                  | Q2                                                                                        | Q3                                                                                                                                                                                                                                                             | Q4                 | Ļ              |  |  |

| No                  | No                                                                                        | No                                                                                                                                                                                                                                                             |                    | No             |  |  |

| operation           | operation                                                                                 | operatio                                                                                                                                                                                                                                                       | on o               | peration       |  |  |

| Example 1           |                                                                                           |                                                                                                                                                                                                                                                                | FLAG, 4<br>PROCESS |                |  |  |

| Case 1:             | Po<br>Fl<br>After Instru<br>Si                                                            | Before Instruction<br>PC = addressHERE<br>FLAG= xxx0 xxxx<br>After Instruction<br>Since FLAG<4>= 0,<br>PC = addressTRUE                                                                                                                                        |                    |                |  |  |

| Case 2:             | Before Inst<br>P(<br>Fl<br>After Instru<br>Si                                             | ruction<br>C = ad<br>LAG= xx<br>Iction                                                                                                                                                                                                                         | ldresshe           | RE<br>X        |  |  |

| Syntax:            | [ <i>label</i> ] BT                                                                                                      | -<br>FSS fb                                                                                                                                                                                                                                                       |                  |  |  |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|--|

| Operands:          | $\begin{bmatrix} aber \end{bmatrix} B \\ 0 \le f \le 127$                                                                | . J.J. 1,D                                                                                                                                                                                                                                                        |                  |  |  |  |

| Operands.          | 0≤1≤127<br>0≤b<7                                                                                                         |                                                                                                                                                                                                                                                                   |                  |  |  |  |

| Operation:         | skip if (f <b>) = 1</b>                                                                                                  |                                                                                                                                                                                                                                                                   |                  |  |  |  |

| Status Affected:   | None                                                                                                                     | None                                                                                                                                                                                                                                                              |                  |  |  |  |

| Encoding:          | 01                                                                                                                       | 01 11bb bfff ffff                                                                                                                                                                                                                                                 |                  |  |  |  |

| Description:       | If bit 'b' is '1<br>tion execut                                                                                          | If bit 'b' in register 'f' is '1' then the next instruction is skipped.<br>If bit 'b' is '1', then the next instruction (fetched during the current instruc-<br>tion execution) is discarded and a NOP is executed instead, making this a<br>2 cycle instruction. |                  |  |  |  |

| Words:             | 1                                                                                                                        |                                                                                                                                                                                                                                                                   |                  |  |  |  |

| Cycles:            | 1(2)                                                                                                                     |                                                                                                                                                                                                                                                                   |                  |  |  |  |

| Q Cycle Activity:  |                                                                                                                          |                                                                                                                                                                                                                                                                   |                  |  |  |  |

| Q1                 | Q2                                                                                                                       | Q3                                                                                                                                                                                                                                                                | Q4               |  |  |  |

| Decode             | Read<br>register 'f'                                                                                                     | Process<br>data                                                                                                                                                                                                                                                   | No<br>operation  |  |  |  |

| If skip (2nd cycle | ):                                                                                                                       |                                                                                                                                                                                                                                                                   |                  |  |  |  |

| Q1                 | Q2                                                                                                                       | Q3                                                                                                                                                                                                                                                                | Q4               |  |  |  |

| No<br>operation    | No<br>operation                                                                                                          | No<br>operation                                                                                                                                                                                                                                                   | No<br>operation  |  |  |  |

| Example 1          |                                                                                                                          | BTFSS FLAG<br>GOTO PROC<br>•                                                                                                                                                                                                                                      | ;, 4<br>ESS_CODE |  |  |  |

| 0 1                | Before Instruction<br>PC = addressHERE<br>FLAG= xxx0 xxxx<br>After Instruction<br>Since FLAG<4>= 0,<br>PC = addressFALSE |                                                                                                                                                                                                                                                                   |                  |  |  |  |

| Case 1:            | After Instru<br>Si                                                                                                       | ction<br>nce FLAG<4>=                                                                                                                                                                                                                                             | = 0,             |  |  |  |

| CALL              | C                                                         | Call Subrout              | tine            |                                                                                                                         |

|-------------------|-----------------------------------------------------------|---------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [label] (                                                 | CALL k                    |                 |                                                                                                                         |

| Operands:         | $0 \le k \le 20$                                          | 47                        |                 |                                                                                                                         |

| Operation:        | $(PC)+1 \rightarrow k \rightarrow PC < 1$<br>(PCLATH < 1) |                           | <12:11>         |                                                                                                                         |

| Status Affected:  | None                                                      |                           |                 |                                                                                                                         |

| Encoding:         | 10                                                        | 0kkk kk                   | kk kkkk         | ]                                                                                                                       |

| Description:      | stack. The                                                | eleven bit in of the PC a | nmediate add    | urn address (PC+1) is pushed onto the<br>dress is loaded into PC bits <10:0>. The<br>m PCLATH<4:3>. CALL is a two cycle |

| Words:            | 1                                                         |                           |                 |                                                                                                                         |

| Cycles:           | 2                                                         |                           |                 |                                                                                                                         |

| Q Cycle Activity: |                                                           |                           |                 |                                                                                                                         |

| 1st cycle:        |                                                           |                           |                 |                                                                                                                         |

| Q1                | Q2                                                        | Q3                        | Q4              | _                                                                                                                       |

| Decode            | Read literal<br>'k'                                       | Process<br>data           | No<br>operation |                                                                                                                         |

| 2nd cycle:        |                                                           |                           |                 | _                                                                                                                       |

| Q1                | Q2                                                        | Q3                        | Q4              | _                                                                                                                       |

| No<br>operation   | No<br>operation                                           | No<br>operation           | No<br>operation |                                                                                                                         |

| Example 1         | HERE<br>Before Ins                                        | CALL THE                  | RE              |                                                                                                                         |

|                   | F<br>After Instr                                          | PC = Addres               |                 |                                                                                                                         |

TOS = Address HERE+1 PC = Address THERE

| CLRF              | Clear f                                                                                                                                                                 |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [ label ] CLRF f                                                                                                                                                        |

| Operands:         | $0 \le f \le 127$                                                                                                                                                       |

| Operation:        | $\begin{array}{l} 00h \rightarrow f \\ 1 \rightarrow Z \end{array}$                                                                                                     |

| Status Affected:  | Z                                                                                                                                                                       |

| Encoding:         | 00 0001 1fff ffff                                                                                                                                                       |

| Description:      | The contents of register 'f' are cleared and the Z bit is set.                                                                                                          |

| Words:            | 1                                                                                                                                                                       |

| Cycles:           | 1                                                                                                                                                                       |

| Q Cycle Activity: |                                                                                                                                                                         |

| Q1                | Q2 Q3 Q4                                                                                                                                                                |

| Decode            | Read Process Write<br>register 'f' data register 'f'                                                                                                                    |

| Example 1         | CLRF FLAG_REG<br>Before Instruction<br>FLAG_REG=0x5A<br>After Instruction<br>FLAG_REG=0x00<br>Z = 1                                                                     |

| Example 2         | CLRF INDF<br>Before Instruction<br>FSR = $0xC2$<br>Contents of Address (FSR)= $0xAA$<br>After Instruction<br>FSR = $0xC2$<br>Contents of Address (FSR)= $0x00$<br>Z = 1 |

| CLRW              |                                                                     | Clear W      | ,        |                      |

|-------------------|---------------------------------------------------------------------|--------------|----------|----------------------|

| Syntax:           | [ label ]                                                           | CLRW         |          |                      |

| Operands:         | None                                                                |              |          |                      |

| Operation:        | $\begin{array}{c} 00h \rightarrow W \\ 1 \rightarrow Z \end{array}$ |              |          |                      |

| Status Affected:  | Z                                                                   |              |          |                      |

| Encoding:         | 00                                                                  | 0001         | 0xxx     | xxxx                 |

| Description:      | W registe                                                           | r is clea    | red. Zei | o bit (Z) is         |

| Words:            | 1                                                                   |              |          |                      |

| Cycles:           | 1                                                                   |              |          |                      |

| Q Cycle Activity: |                                                                     |              |          |                      |

| Q1                | Q2                                                                  | Q3           | G        | 24                   |

| Decode            | Read<br>register 'f'                                                | Proce<br>dat |          | Write<br>egister 'W' |

|                   |                                                                     |              |          | -                    |

| Example 1         | CLRW                                                                |              |          |                      |

Before Instruction W = 0x5AAfter Instruction W = 0x00Z = 1

| CLRWD             | Clear Watchdog Timer                                                                                                                                           |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:           | [ label ] CLRWDT                                                                                                                                               |  |  |  |  |

| Operands:         | None                                                                                                                                                           |  |  |  |  |

| Operation:        | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \mbox{ prescaler count,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$ |  |  |  |  |

| Status Affected:  | TO, PD                                                                                                                                                         |  |  |  |  |

| Encoding:         | 00 0000 0110 0100                                                                                                                                              |  |  |  |  |

| Description:      | CLRWDT instruction clears the Watchdog Timer. It also clears the pres<br>caler count of the WDT. Status bits TO and PD are set.                                |  |  |  |  |

| Words:            | 1                                                                                                                                                              |  |  |  |  |

| Cycles:           | 1                                                                                                                                                              |  |  |  |  |

| Q Cycle Activity: |                                                                                                                                                                |  |  |  |  |

| Q1                | Q2 Q3 Q4                                                                                                                                                       |  |  |  |  |

| Decode            | No     Process     Clear       operation     data     WDT       Counter     Counter                                                                            |  |  |  |  |

| Example 1         | CLRWDT                                                                                                                                                         |  |  |  |  |

|                   | Before Instruction<br>WDT counter= x<br>WDT prescaler =1:128<br>After Instruction<br>WDT counter=0x00                                                          |  |  |  |  |

|                   | WDT prescaler count=0<br>$\overline{TO} = 1$<br>$\overline{PD} = 1$<br>WDT prescaler =1:128                                                                    |  |  |  |  |

Note: The CLRWDT instruction does not affect the assignment of the WDT prescaler.

| COMF              | Complement f                                                                                                                                     |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | [label] COMF f,d                                                                                                                                 |

| Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                               |

| Operation:        | $(\bar{f}) \rightarrow destination$                                                                                                              |

| Status Affected:  | Z                                                                                                                                                |

| Encoding:         | 00 1001 dfff ffff                                                                                                                                |

| Description:      | The contents of register 'f' are 1's complemented. If 'd' is 0 the result is stored in W. If 'd' is 1 the result is stored back in register 'f'. |

| Words:            | 1                                                                                                                                                |

| Cycles:           | 1                                                                                                                                                |

| Q Cycle Activity: |                                                                                                                                                  |

| Q1                | Q2 Q3 Q4                                                                                                                                         |

| Decode            | Read     Process     Write to       register 'f'     data     destination                                                                        |

|                   |                                                                                                                                                  |

| Example 1         | COMF REG1, 0                                                                                                                                     |

|                   | Before Instruction                                                                                                                               |